6502 Microprocessor Family

# 6502 Microprocessor Family

Notes about assembly language

Peter Mount, Area51.dev & Contributors

CC BY-SA

# 6502 Microprocessor Family

Notes about assembly language

Title6502 Microprocessor FamilySubtitleNotes about assembly languageAuthorPeter Mount, Area51.dev & ContributorsCopyright CC BY-SA

# CC BY-SA version 4.0 license

### You are free to:

- 1. Share copy and redistribute the material in any medium or format

- 2. Adapt remix, transform, and build upon the material or any purpose, even commercially.

This license is acceptable for Free Cultural Works.

The licensor cannot revoke these freedoms as long as you follow the license terms.

### Under the following terms:

- 1. **Attribution** You must give appropriate credit, provide a link to the license, and indicate if changes were made. You may do so in any reasonable manner, but not in any way that suggests the licensor endorses you or your use.

- 2. **ShareAlike** If you remix, transform, or build upon the material, you must distribute your contributions under the same license as the original.

- 3. No additional restrictions You may not apply legal terms or technological measures that legally restrict others from doing anything the license permits.

### Notices:

You do not have to comply with the license for elements of the material in the public domain or where your use is permitted by an applicable exception or limitation.

No warranties are given. The license may not give you all of the permissions necessary for your intended use. For example, other rights such as publicity, privacy, or moral rights may limit how you use the material.

You can read the full license here: https://creativecommons.org/licenses/by-sa/4.0/

# **Table of Contents**

1 <u>Opcodes</u> 1.1 Arithmetic 1.1.1 ADC Add With Carry 1.1.2 Decrement 1.1.3 Increment 1.1.4 SBC Subtract with Borrow from Accumulator 1.2 Binary operations 1.2.1 AND 1.2.2 BIT 1.2.3 EOR - Exclusive OR 1.2.4 ORA - OR Accumulator with memory 1.2.5 Rotate Bits 1.2.6 TRB & TSB 1.3 Program Flow 1.3.1 <u>Flags</u> 1.3.2 Compare Accumulator 1.3.3 Compare Index Register 1.3.4 Branch 1.3.5 Jump to location 1.3.6 Subroutines 1.4 <u>Registers</u> 1.4.1 <u>LDA</u> 1.4.2 <u>LDX</u> 1.4.3 LDY 1.4.4 <u>STA</u> 1.4.5 <u>STX</u> 1.4.6 <u>STY</u> 1.4.7 <u>STZ</u> 1.4.8 Transfer 1.5 <u>Stack</u> 1.5.1 Pull 1.5.2 <u>Push</u> 1.6 Interrupts 1.6.1 BRK - Software Break 1.6.1.1 BRK on the BBC Micro & Acorn Electron 1.6.2 COP - Co-Processor Enable 1.6.3 <u>RTI</u> 1.6.4 WAI - Wait for Interrupt 1.7 Miscellaneous Instructions 1.7.1 <u>Block Move</u> 1.7.2 XCE 1.7.3 <u>NOP</u> 1.7.4 Reserved 1.7.5 STP - Stop Processor 2 <u>reference</u> 2.1 Instruction List by name 2.2 Instruction List by opcode

2.3 Opcode Matrix

This section covers assembly language for the 6502 Microprocessor family including the 6510, 65C02 & 65816 processors.

## 1 - Opcodes

Instruction Set In this section we cover every available instruction for both 8-bit & 16-bit processors.

# 1.1 - Arithmetic

Arithmetic operations

# 1.1.1 - ADC Add With Carry

### Add With Carry

Adds the data in the operand with the contents of the accumulator. Add 1 to the result if the carry flag is set. Store the final result in the accumulator.

### Binary/Decimal mode

If the d flag is clear then binary addition is performed. If the d flag set then Binary Coded Decimal (BCD) addition is performed.

### Data size

On all processors, the data added from memory is 8-bit. However, for 16-bit processors with the m flag is clear then the data added is 16-bit with the low-order 8-bits at the effective address and the high-order 8-bits at the effective address plus one.

### Multi-precision arithmetic

In multi-precision (multi-word) arithmetic, the carry flag should be cleared before the low-order words are added. The addition will generate a new carry flag value based on that addition which will then be passed on to the next word.

For example, to add 1 to a 16-bit value at &70 on 8-bit processors:

```

1CLC; Clear carry before first addition2LDA &70; Add 1 to low-order byte3ADC #14STA &705LDA &71; Add 0 to high order byte6ADC #0; This will add 1 if carry was set7STA &71; in the low-order byte

```

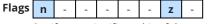

Flags Affected

- Flags n v - z c

- **n** Set if most-significant bit of result is set

- v Set if signed overflow

- **z** Set if result is zero

- c Set if unsigned overflow, clear if valid unsigned result

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                    |                                     |

|-----------------------|--------|--------|---------|-------|----------------|-------------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles                  | Addressing Mode                     |

| ADC #const            | 69     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2, 5</sup>       | Immediate                           |

| ADC addr              | 6D     | х      | х       | х     | 3              | 4 <sup>2, 5</sup>       | Absolute                            |

| ADC long              | 6F     |        |         | х     | 4              | 5 <sup>2, 5</sup>       | Absolute Long                       |

| ADC dp                | 65     | х      | х       | х     | 2              | 3 <sup>2, 3, 5</sup>    | Direct Page                         |

| ADC ( <i>dp</i> )     | 72     |        | х       | x     | 2              | 5 <sup>2, 3, 5</sup>    | Direct Page Indirect                |

| ADC [ <i>dp</i> ]     | 67     |        |         | х     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indirect Long           |

| ADC addr,X            | 7D     | х      | х       | х     | 3              | 4 <sup>2, 4, 5</sup>    | Absolute Indexed X                  |

| ADC long,X            | 7F     |        |         | х     | 4              | 5 <sup>2, 5</sup>       | Absolute Long Indexed X             |

| ADC addr,Y            | 79     | х      | х       | х     | 3              | 4 <sup>2, 4, 5</sup>    | Absolute Indexed Y                  |

| ADC dp,X              | 75     | х      | х       | x     | 2              | 4 <sup>2, 3, 5</sup>    | Direct Page Indexed X               |

| ADC ( <i>dp</i> ,X)   | 61     | х      | х       | х     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indexed Indirect X      |

| ADC ( <i>dp</i> ),Y   | 71     | х      | х       | х     | 2              | 5 <sup>2, 3, 4, 5</sup> | Direct Page Indirect Indexed Y      |

| ADC [ <i>dp</i> ],Y   | 77     |        |         | х     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indirect Long Indexed Y |

| ADC sr,S              | 63     |        |         | x     | 2              | 4 <sup>2, 5</sup>       | Stack Relative                      |

| ADC ( <i>sr</i> ,S),Y | 73     |        |         | х     | 2              | 7 <sup>2, 5</sup>       | Stack Relative Indirect Indexed Y   |

### Notes:

- 1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

- 3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

- 4. Add 1 cycle if adding index crosses a page boundary

- 5. 65C02: Add 1 cycle if d=1

# 1.1.2 - Decrement

Decrement by one a register or a memory location

The decrement instructions add one to either a register or a memory location.

Unlike subtracting 1 with ADC, these instructions does not use the Carry flag in any way. You can test for wraparound only by testing after every decrement to see if the result is zero or negative.

The d flag does not affect these instructions. The decrement is always in binary mode.

For all processors, the decrement is an 8-bit operation unless m=0 on the 65816 in which case the decrement is 16-bit.

## DEC - Decrement

Decrement by 1 the contents of the memory location or accumulator.

### DEX - Decrement Index Register X

Decrement by 1 the X index register.

## DEY - Decrement Index Register Y

Decrement by 1 the Y index register.

#### Flags Affected

| Flags | n | - | - | - | - | - | z | - |  |

|-------|---|---|---|---|---|---|---|---|--|

- **n** Set if most significant bit of the result is set

- z Set if result is zero

### Instructions

|            | Opcode | Availab | le on: |       | # of  | # of              |                       |  |

|------------|--------|---------|--------|-------|-------|-------------------|-----------------------|--|

| Syntax     | (hex)  | 6502    | 65C02  | 65816 | bytes | cycles            | Addressing Mode       |  |

| DEC A      | ЗA     |         | х      | х     | 1     | 2                 | Accumulator           |  |

| DEC addr   | CE     | х       | х      | х     | 3     | 6 <sup>1</sup>    | Absolute              |  |

| DEC dp     | C6     | х       | х      | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |  |

| DEC addr,X | DE     | х       | х      | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |  |

| DEC dp,X   | D6     | х       | х      | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |  |

| DEX        | CA     | х       | х      | х     | 1     | 2                 | Implied               |  |

| DEY        | 88     | х       | х      | х     | 1     | 2                 | Implied               |  |

### Notes:

- 1. 65816: Add 2 cycles if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if low byte of Direct Page register is not 0

3. 65C02: Subtract 1 cycle if no page boundary is crossed

# 1.1.3 - Increment

Increment by one a register or a memory location

The increment instructions add one to either a register or a memory location.

Unlike adding 1 with ADC, these instructions does not use the Carry flag in any way. You can test for wraparound only by testing after every increment to see if the result is zero or positive.

The d flag does not affect these instructions. The increment is always in binary mode.

For all processors, the increment is an 8-bit operation unless m=0 on the 65816 in which case the increment is 16-bit.

### INC - Increment

Increment by 1 the contents of the memory location or accumulator.

### INX - Increment Index Register X

Increment by 1 the X index register.

## INY - Increment Index Register Y

Increment by 1 the Y index register.

#### Flags Affected

| Flags | n | - | - | - | - | - | z | 1 |  |

|-------|---|---|---|---|---|---|---|---|--|

- n Set if most significant bit of the result is set

- z Set if result is zero

#### Instructions

|            | Opcode | Availab | le on: |       | # of  | # of              |                       |

|------------|--------|---------|--------|-------|-------|-------------------|-----------------------|

| Syntax     | (hex)  | 6502    | 65C02  | 65816 | bytes | cycles            | Addressing Mode       |

| INC A      | 1A     |         | х      | х     | 1     | 2                 | Accumulator           |

| INC addr   | EE     | х       | х      | х     | 3     | 6 <sup>1</sup>    | Absolute              |

| INC dp     | E6     | х       | х      | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |

| INC addr,X | FE     | х       | х      | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |

| INC dp,X   | F6     | x       | х      | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |

| INX        | E8     | х       | х      | х     | 1     | 2                 | Implied               |

| INY        | C8     | х       | х      | х     | 1     | 2                 | Implied               |

### Notes:

- 1. 65816: Add 2 cycles if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if low byte of Direct Page register is not 0

3. 65C02: Subtract 1 cycle if no page boundary is crossed

# 1.1.4 - SBC Subtract with Borrow from Accumulator

### Subtract with Borrow

Subtracts the data in the operand with the contents of the accumulator. Subtract 1 from the result if the carry flag is clear. Store the final result in the accumulator.

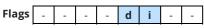

### Binary/Decimal mode

If the d flag is clear then binary subtraction is performed. If the d flag set then Binary Coded Decimal (BCD) subtraction is performed.

### Data size

On all processors, the data subtracted from memory is 8-bit. However, for 16-bit processors with the m flag is clear then the data subtracted is 16-bit with the low-order 8-bits at the effective address and the high-order 8-bits at the effective address plus one.

### Multi-precision arithmetic

In multi-precision (multi-word) arithmetic, the carry flag should be set before the low-order words are subtracted. The subtraction will generate a new carry flag value based on that subtraction which will then be passed on to the next word.

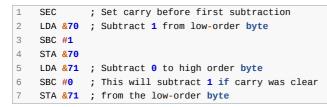

For example, to subtract 1 from a 16-bit value at &70 on 8-bit processors:

#### Flags Affected

### Flags n v - - - z c

- **n** Set if most-significant bit of result is set

- **v** Set if signed overflow

- **z** Set if result is zero

- c Set if unsigned borrow not required, clear if required

#### Instructions

|                     | Opcode | Availa | ble on: |       | # of           | # of                    |                                     |

|---------------------|--------|--------|---------|-------|----------------|-------------------------|-------------------------------------|

| Syntax              | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles                  | Addressing Mode                     |

| SBC #const          | E9     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2, 5</sup>       | Immediate                           |

| SBC addr            | ED     | х      | х       | х     | 3              | 4 <sup>2, 5</sup>       | Absolute                            |

| SBC long            | EF     |        |         | х     | 4              | 5 <sup>2, 5</sup>       | Absolute Long                       |

| SBC dp              | E5     | х      | х       | х     | 2              | 3 <sup>2, 3, 5</sup>    | Direct Page                         |

| SBC ( <i>dp</i> )   | F2     |        | х       | х     | 2              | 5 <sup>2, 3, 5</sup>    | Direct Page Indirect                |

| SBC [dp]            | E7     |        |         | х     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indirect Long           |

| SBC addr,X          | FD     | х      | х       | х     | 3              | 4 <sup>2, 4, 5</sup>    | Absolute Indexed X                  |

| SBC long,X          | FF     |        |         | х     | 4              | 5 <sup>2, 5</sup>       | Absolute Long Indexed X             |

| SBC addr,Y          | F9     | х      | x       | x     | 3              | 4 <sup>2, 4, 5</sup>    | Absolute Indexed Y                  |

| SBC dp,X            | F5     | х      | х       | х     | 2              | 4 <sup>2, 3, 5</sup>    | Direct Page Indexed X               |

| SBC (dp,X)          | E1     | х      | х       | х     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indexed Indirect X      |

| SBC ( <i>dp</i> ),Y | F1     | х      | х       | х     | 2              | 5 <sup>2, 3, 4, 5</sup> | Direct Page Indirect Indexed Y      |

| SBC [ <i>dp</i> ],Y | F7     |        |         | x     | 2              | 6 <sup>2, 3, 5</sup>    | Direct Page Indirect Long Indexed Y |

| SBC sr,S            | E3     |        |         | х     | 2              | 4 <sup>2, 5</sup>       | Stack Relative                      |

| SBC (sr,S),Y        | F3     |        |         | х     | 2              | 7 <sup>2, 5</sup>       | Stack Relative Indirect Indexed Y   |

### Notes:

- 1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

- 3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

- 4. Add 1 cycle if adding index crosses a page boundary

5. 65C02: Add 1 cycle if d=1

# 1.2 - Binary operations

Operations that work in Binary or individual Bits

## 1.2.1 - AND

### And Accumulator with Memory

AND performs a logical And of the value in the accumulator with that of the memory location with the result stored in the accumulator.

The result will be each bit in the accumulator will be set ONLY if that same bit was set in the original accumulator value and the memory. If the bits were different then the resultant bit will be 0.

| :               | Second | Operand |

|-----------------|--------|---------|

|                 | 0      | 1       |

| First Operand 0 | 0      | 0       |

| 1               | 0      | 1       |

AND truth table

For 8-bit processors n has the value of bit 7 and v the value of bit 6 of the memory location.

For 16-bit processors, when m=0, n has the value of bit 15 and v the value of bit 14 of the memory location.

Second it performs a logical AND of the memory and the accumulator. If the result is zero the z flag is set.

In both operations, the contents of the accumulator and memory are not modified.

Flags Affected

|       | - |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|---|

| Flags | n | - | - | - | - | - | z | - |

- **n** Set if most significant bit of result is set

- **z** Set if result is zero, otherwise clear

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                 |                                     |

|-----------------------|--------|--------|---------|-------|----------------|----------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles               | Addressing Mode                     |

| AND #const            | 29     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2</sup>       | Immediate                           |

| AND addr              | 2D     | х      | х       | х     | 3              | 4 <sup>2</sup>       | Absolute                            |

| AND long              | 2F     |        |         | x     | 4              | 5 <sup>2</sup>       | Absolute Long                       |

| AND dp                | 25     | х      | х       | х     | 2              | 3 <sup>2, 3</sup>    | Direct Page                         |

| AND ( <i>dp</i> )     | 32     |        | х       | x     | 2              | 5 <sup>2, 3</sup>    | Direct Page Indirect                |

| AND [dp]              | 27     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long           |

| AND addr,X            | 3D     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed X                  |

| AND long,X            | 3F     |        |         | х     | 4              | 5 <sup>2</sup>       | Absolute Long Indexed X             |

| AND addr,Y            | 39     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed Y                  |

| AND <i>dp</i> ,X      | 35     | х      | х       | x     | 2              | 4 <sup>2, 3</sup>    | Direct Page Indexed X               |

| AND ( <i>dp</i> ,X)   | 21     | х      | х       | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indexed Indirect X      |

| AND ( <i>dp</i> ),Y   | 31     | х      | х       | x     | 2              | 5 <sup>2, 3, 4</sup> | Direct Page Indirect Indexed Y      |

| AND [ <i>dp</i> ],Y   | 37     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long Indexed Y |

| AND sr,S              | 23     |        |         | x     | 2              | 4 <sup>2</sup>       | Stack Relative                      |

| AND ( <i>sr</i> ,S),Y | 33     |        |         | x     | 2              | 7 <sup>2</sup>       | Stack Relative Indirect Indexed Y   |

### Notes:

- 1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

- 3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

# 1.2.2 - BIT

#### Test Memory Bits against Accumulator

Bit is a dual-purpose instruction which performs operations against the accumulator and memory. It is usually used immediately preceding a conditional branch instruction

First it set's the n flag to reflect the value of the high bit of the data in memory and the v flag to the next-to-highest bit of that data.

For 8-bit processors n has the value of bit 7 and v the value of bit 6 of the memory location.

For 16-bit processors, when m=0, n has the value of bit 15 and v the value of bit 14 of the memory location.

Second it performs a logical AND of the memory and the accumulator. If the result is zero the z flag is set.

In both operations, the contents of the accumulator and memory are not modified.

#### Flags Affected

### Flags n v - - - z -

- **n** Takes value of most significant bit of memory data, not in immediate addressing

- ${f v}$  Takes value of the next-to-highest bit of memory data, not in immediate addressing

- z Set if logical AND of memory & accumulator is zero, otherwise clear

### Instructions

|                  | Opcode | Availab | le on: |       | # of           | # of              |                       |

|------------------|--------|---------|--------|-------|----------------|-------------------|-----------------------|

| Syntax           | (hex)  | 6502    | 65C02  | 65816 | bytes          | cycles            | Addressing Mode       |

| BIT #const       | 89     |         | х      | х     | 2 <sup>1</sup> | 2 <sup>2</sup>    | Immediate             |

| BIT addr         | 2C     | х       | х      | х     | 3              | 4 <sup>2</sup>    | Absolute              |

| BIT dp           | 24     | х       | х      | х     | 2              | 5 <sup>2, 3</sup> | Direct Page           |

| BIT addr,X       | 3C     |         | х      | х     | 3              | 4 <sup>2, 4</sup> | Absolute Indexed X    |

| BIT <i>dp</i> ,X | 34     |         | х      | х     | 2              | 4 <sup>2, 3</sup> | Direct Page Indexed X |

#### Notes:

1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

2. 658116: Add 1 cycle if m=0 (16-bit memory/accumulator)

3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

# 1.2.3 - EOR - Exclusive OR

#### Exclusive-OR Accumulator with Memory

EOR performs a bitwise logical Exclusive-OR of the value in the accumulator with that of the memory location with the result stored in the accumulator.

The result will be each bit in the accumulator will be set ONLY if that same bit in the original accumulator value and the memory differ. If the bits were the same then the resultant bit will be 0.

|                 | Second | Operand |

|-----------------|--------|---------|

|                 | 0      | 1       |

| First Operand 0 | 0      | 1       |

| 1               | 1      | 0       |

Exclusive OR truth table

For 8-bit processors n has the value of bit 7 and v the value of bit 6 of the memory location.

For 16-bit processors, when m=0, n has the value of bit 15 and v the value of bit 14 of the memory location.

Second it performs a logical AND of the memory and the accumulator. If the result is zero the z flag is set.

In both operations, the contents of the accumulator and memory are not modified.

### Flags Affected

| Flags | n | - | - | - | - | - | z | - |  |

|-------|---|---|---|---|---|---|---|---|--|

|       |   |   |   |   |   |   |   |   |  |

**n** Set if most significant bit of result is set

z Set if result is zero, otherwise clear

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                 |                                     |

|-----------------------|--------|--------|---------|-------|----------------|----------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles               | Addressing Mode                     |

| EOR #const            | 49     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2</sup>       | Immediate                           |

| EOR addr              | 4D     | х      | х       | х     | 3              | 4 <sup>2</sup>       | Absolute                            |

| EOR long              | 4F     |        |         | х     | 4              | 5 <sup>2</sup>       | Absolute Long                       |

| EOR dp                | 45     | х      | х       | х     | 2              | 3 <sup>2, 3</sup>    | Direct Page                         |

| EOR ( <i>dp</i> )     | 52     |        | х       | х     | 2              | 5 <sup>2, 3</sup>    | Direct Page Indirect                |

| EOR [ <i>dp</i> ]     | 47     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long           |

| EOR addr,X            | 5D     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed X                  |

| EOR long,X            | 5F     |        |         | х     | 4              | 5 <sup>2</sup>       | Absolute Long Indexed X             |

| EOR addr,Y            | 59     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed Y                  |

| EOR <i>dp</i> ,X      | 55     | х      | х       | х     | 2              | 4 <sup>2, 3</sup>    | Direct Page Indexed X               |

| EOR ( <i>dp</i> ,X)   | 41     | х      | х       | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indexed Indirect X      |

| EOR ( <i>dp</i> ),Y   | 51     | х      | х       | х     | 2              | 5 <sup>2, 3, 4</sup> | Direct Page Indirect Indexed Y      |

| EOR [ <i>dp</i> ],Y   | 57     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long Indexed Y |

| EOR sr,S              | 43     |        |         | х     | 2              | 4 <sup>2</sup>       | Stack Relative                      |

| EOR ( <i>sr</i> ,S),Y | 53     |        |         | х     | 2              | 7 <sup>2</sup>       | Stack Relative Indirect Indexed Y   |

| EOR ( <i>sr</i> ,S),Y | 53     |        |         | х     | 2              | 7 <sup>2</sup>       | Stack Relative Indirect Indexed Y   |

#### Notes:

1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

# 1.2.4 - ORA - OR Accumulator with memory

### OR Accumulator with Memory

ORA performs a bitwise logical OR of the value in the accumulator with that of the memory location with the result stored in the accumulator.

The result will be each bit in the accumulator will be set if either the same bit in the original accumulator value and the memory are set.

|                 | Second | Operand |

|-----------------|--------|---------|

|                 | 0      | 1       |

| First Operand 0 | 0      | 1       |

| 1               | 1      | 1       |

OR truth table

For 8-bit processors n has the value of bit 7 and v the value of bit 6 of the memory location.

For 16-bit processors, when m=0, n has the value of bit 15 and v the value of bit 14 of the memory location.

Second it performs a logical AND of the memory and the accumulator. If the result is zero the z flag is set.

In both operations, the contents of the accumulator and memory are not modified.

#### Flags Affected

| Flags | n | - | - | - | - | - | z | - |  |

|-------|---|---|---|---|---|---|---|---|--|

|       |   |   |   |   |   |   |   |   |  |

**n** Set if most significant bit of result is set

z Set if result is zero, otherwise clear

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                 |                                     |

|-----------------------|--------|--------|---------|-------|----------------|----------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles               | Addressing Mode                     |

| ORA #const            | 09     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2</sup>       | Immediate                           |

| ORA addr              | 0D     | х      | х       | х     | 3              | 4 <sup>2</sup>       | Absolute                            |

| ORA long              | 0F     |        |         | х     | 4              | 5 <sup>2</sup>       | Absolute Long                       |

| ORA dp                | 05     | х      | х       | х     | 2              | 3 <sup>2, 3</sup>    | Direct Page                         |

| ORA ( <i>dp</i> )     | 12     |        | х       | х     | 2              | 5 <sup>2, 3</sup>    | Direct Page Indirect                |

| ORA [ <i>dp</i> ]     | 07     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long           |

| ORA addr,X            | 1D     | х      | х       | x     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed X                  |

| ORA long,X            | 1F     |        |         | x     | 4              | 5 <sup>2</sup>       | Absolute Long Indexed X             |

| ORA addr,Y            | 19     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed Y                  |

| ORA <i>dp</i> ,X      | 15     | х      | х       | x     | 2              | 4 <sup>2, 3</sup>    | Direct Page Indexed X               |

| ORA ( <i>dp</i> ,X)   | 01     | х      | х       | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indexed Indirect X      |

| ORA ( <i>dp</i> ),Y   | 11     | х      | х       | х     | 2              | 5 <sup>2, 3, 4</sup> | Direct Page Indirect Indexed Y      |

| ORA [ <i>dp</i> ],Y   | 17     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long Indexed Y |

| ORA <i>sr</i> ,S      | 03     |        |         | x     | 2              | 4 <sup>2</sup>       | Stack Relative                      |

| ORA ( <i>sr</i> ,S),Y | 13     |        |         | х     | 2              | 7 <sup>2</sup>       | Stack Relative Indirect Indexed Y   |

|                       |        |        |         |       |                |                      |                                     |

#### Notes:

1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

# 1.2.5 - Rotate Bits

Test Memory Bits against Accumulator

The rotate instructions shifts the contents of the accumulator or memory location one bit either to the left or right.

The ROL & ROR instructions will shift in the carry flag into the value. The ASL & LSR instructions shift in 0. The carry flag is set to the bit that was shifted out of the value.

On all processors the data shifted is 8 bits

On the 65816 with m=0, the data shifted is 16 bits.

| Operation              | Opcode | e 76543210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift left             | ASL    | C <b>←←←←</b> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Shift left with carry  | ROL    | C <b>←←←←←</b> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Shift right            | LSR    | $0 {\color{red} \rightarrow \rightarrow \rightarrow \rightarrow \rightarrow \rightarrow \rightarrow \rightarrow } C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Shift right with carry | /ROR   | $C { \longrightarrow } { \longrightarrow } { \longrightarrow } { \longrightarrow } { \land } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } { : } $ : } :  : : : : : : : : : : : : : |

Effect on memory for 8 bit operations.

## ASL - Shift Memory or Accumulator Left

Shift the value left one bit. The left most bit is transferred into the carry flag. The right most bit is cleared.

The arithmetic result of the operation is an unsigned multiplication by two.

### LSR - Logical Shift Memory or Accumulator Right

Shift the value right one bit. The right most bit is transferred into the carry flag. The left most bit is cleared.

The arithmetic result of the operation is an unsigned division by two.

### ROL - Rotate Memory or Accumulator Left

Shift the value left one bit. The right most bit is set to the initial value of the carry flag. The left most bit is transferred into the carry flag.

## ROR - Rotate Memory or Accumulator Right

Shift the value right one bit. The left most bit is set to the initial value of the carry flag. The right most bit is transferred into the carry flag.

## Multi-word shifts

These instructions can be combined to handle multiple word values:

### Multi-word shift left

To shift left multiple words, use ASL for the first operation then ROL for the subsequent words.

```

1 ; Shift 16-bit value at &70 left 1 bit.

2 ; This is effectively a multiplication by 2

3 ASL &70 ; Shift left low-order byte

4 ROL &71 ; Shift left high-order byte

5 ; Carry will be set if we overflowed

6

```

For higher precision simply add an additional ROL for the next order byte.

### Multi-word shift right

To shift right multiple words, use LSR for the first operation then ROR for the subsequent words. Unlike shifting left, here we have to start with the high-order byte first.

```

; Shift 16-bit value at &70 right 1 bit.

; This is effectively a division by 2

LSR &71 ; Shift right high-order byte

ROR &70 ; Shift right low-order byte

; Carry will have the remainder

```

For higher precision just start the LSR on the higher order byte & use ROL for each lower order.

### Flags Affected

### Flags n - - - - z c

- ${\bm n} \quad {\rm Set \ if \ the \ most \ significant \ bit \ of \ the \ result \ is \ set}$

- **z** Set if the result is zero

- **c** The value of the bit shifted out of the result

### Instructions

|                  | Opcode | Availab | ole on: |       | # of  | # of              |                       |

|------------------|--------|---------|---------|-------|-------|-------------------|-----------------------|

| Syntax           | (hex)  | 6502    | 65C02   | 65816 | bytes | cycles            | Addressing Mode       |

| ASL A            | 0A     | х       | х       | х     | 1     | 2                 | Accumulator           |

| ASL addr         | 0E     | х       | х       | х     | 3     | 6                 | Absolute              |

| ASL dp           | 06     | х       | х       | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |

| ASL addr,X       | 1E     | х       | х       | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |

| ASL dp,X         | 16     | х       | х       | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |

| LSR A            | 4A     | х       | х       | х     | 1     | 2                 | Accumulator           |

| LSR addr         | 4E     | х       | х       | х     | 3     | 6                 | Absolute              |

| LSR dp           | 46     | х       | х       | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |

| LSR addr,X       | 5E     | х       | х       | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |

| LSR dp,X         | 56     | х       | х       | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |

| ROL A            | 2A     | х       | х       | х     | 1     | 2                 | Accumulator           |

| ROL addr         | 2E     | х       | х       | х     | 3     | 6                 | Absolute              |

| ROL dp           | 26     | х       | х       | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |

| ROL addr,X       | 3E     | х       | х       | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |

| ROL dp,X         | 36     | х       | х       | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |

| ROR A            | 6A     | х       | х       | х     | 1     | 2                 | Accumulator           |

| ROR addr         | 6E     | х       | х       | х     | 3     | 6                 | Absolute              |

| ROR <i>dp</i>    | 66     | х       | х       | х     | 2     | 5 <sup>1, 2</sup> | Direct Page           |

| ROR addr,X       | 7E     | х       | х       | х     | 3     | 7 <sup>1, 3</sup> | Absolute Indexed X    |

| ROR <i>dp</i> ,X | 76     | х       | х       | х     | 2     | 6 <sup>1, 2</sup> | Direct Page Indexed X |

|                  |        |         |         |       |       |                   |                       |

### Notes:

- 1. 65816: Add 2 cycles if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if low byte of Direct Page register is not 0

- 3. 65C02: Subtract 1 cycle if no page boundary is crossed

# 1.2.6 - TRB & TSB

Test & Set/Reset Memory Bits against Accumulator

## TRB - Test & Reset memory against Accumulator

TRB logically AND's the *complement* of the accumulator with the data at an address and stores the result in that address.

This has the effect of clearing each memory bit which is set in the accumulator, leaving the other bits unchanged.

The z flag is set based on a different operation. It's set if the memory location once set logically AND the accumulator (not it's compliment) is zero.

For 8-bit processors or when m=1, the values in the accumulator & memory are 8-bit.

For 16-bit processors, when m=0, the values in the accumulator & memory are 16-bit.

## TSB - Test & Set memory against Accumulator

TSB is identical to TRB except it sets the bits defined in the Accumulator not reset them.

#### Flags Affected

| Flags | - | - | - | - | - | - | z | - |  |

|-------|---|---|---|---|---|---|---|---|--|

z Set if logical AND of memory & accumulator is zero, otherwise clear

#### Instructions

|          | Opcode | Availabl | e on: |       | # of  | # of              |                 |

|----------|--------|----------|-------|-------|-------|-------------------|-----------------|

| Syntax   | (hex)  | 6502     | 65C02 | 65816 | bytes | cycles            | Addressing Mode |

| TRB addr | 1C     |          | х     | х     | 3     | 6 <sup>1</sup>    | Absolute        |

| TRB dp   | 14     |          | х     | х     | 2     | 5 <sup>1, 2</sup> | Direct Page     |

| TSB addr | 0C     |          | х     | х     | 3     | 6 <sup>1</sup>    | Absolute        |

| TSB dp   | 04     |          | х     | х     | 2     | 5 <sup>1, 2</sup> | Direct Page     |

#### Notes:

1. 65816: Add 2 cycles if m=0 (16-bit memory/accumulator)

# 1.3 - Program Flow

Branch & Jumps

# 1.3.1 - Flags

Flag manipulation

The flag instructions manipulate some of the flags in the status register.

### CLC - Clear Carry Flag

CLC is used prior to addition with the ADC instruction to keep the carry flag affecting the result.

On the 6502 a CLC before a BCC instruction can be used to implement a branch always, which is relocatable. This is unnecessary since the 65C02 with it's BRA instruction.

On the 16-bit processors a CLC followed by XCE instruction is used to switch the 65802 & 65816 processors into native mode.

### SEC - Set Carry Flag

SEC is used prior to subtraction using the SBC instruction to keep the carry flag affecting the result.

On the 16-bit processors a SEC followed by XCE instruction is used to switch the 65802 & 65816 processors into 6502 emulation mode.

### CLD - Clear Decimal Mode

CLD is used to switch the processors into binary mode so that the ADC & SBC instructions will perform binary not BCD arithmetic.

### SED - Set Decimal Mode

SED is used to switch the processors into decimal mode so that the ADC & SBC instructions will perform BCD not binary arithmetic.

### CLI - Clear Interrupt Disable Flag

CLI is used to re-enable hardware interrupts.

When the processor starts the interrupt handler it sets the i flag to prevent another interrupt to occur during that handler. If the handler want's to allow interrupts to happen whilst it's handling a previous one it can use CLI to re-enable them. The handler doesn't need to use CLI as the RTI (ReTurn from Interrupt) instruction will clear the i flag automatically.

In user code, CLI can be used to re-enable interrupts after an SEI instruction. This is usually used during time-critical code or code that cannot be interrupted.

### SEI - Clear Interrupt Disable Flag

SEI is used to disable hardware interrupts.

When the i bit is set, maskable hardware interrupts are ignored. When the processor starts the interrupt handler it sets the i flag to prevent another interrupt to occur during that handler. If the handler want's to allow interrupts to happen whilst it's handling a previous one it can use CLI to re-enable them. The handler doesn't need to use CLI as the RTI (ReTurn from Interrupt) instruction will clear the i flag automatically.

In user code, SEI can be used to disable interrupts when it needs to run time-critical code or code that cannot be interrupted. It should then use CLI once it's finished that time-critical code.

### CLV - Clear Overflow Flag

CLV clears the overflow flag.

Unlike other clear flag instructions, there is no set overflow flag available. The only way the overflow flag can be set is either:

- The BIT instruction will set overflow if bit 6 of the mask & memory is set

- The 65816 REP instruction can clear the overflow

- Use the Overflow pin on the processor. This is rarely used & is often not even connected.

On the 6502 a CLC before a BVC instruction can be used to implement a branch always, which is relocatable. This is unnecessary since the 65C02 with it's BRA instruction.

### **REP** - Reset Status Bits

For each bit set in the operand byte, reset the corresponding bit in the status register. For each bit not set in the operand byte leaves the corresponding bit unchanged.

This instruction lets you clear any flag or flags in a single instruction. It is the only direct means of resetting the m & x flags.

In 6502 emulation mode (e=1) neither the b flag or bit 5 (the 6502's non-flag bit) is affected by this instruction.

|                         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------|---|---|---|---|---|---|---|---|

| 6502 emulation mode e=1 | n | V |   |   | d | i | Z | с |

| 65816 native mode e=0   | n | V | m | х | d | i | Z | С |

Flags Affected

### SEP - Set Status Bits

For each bit set in the operand byte, set the corresponding bit in the status register. For each bit not set in the operand byte leaves the corresponding bit unchanged.

This instruction lets you set any flag or flags in a single instruction. It is the only direct means of setting the m & x flags.

In 6502 emulation mode (e=1) neither the b flag or bit 5 (the 6502's non-flag bit) is affected by this instruction.

The bit's in the operand & their relationship with the status register is the same as the REP instruction.

#### Instructions

|            |                             | Opcode | Available on: |       |       | # of  | # of   |                 |  |

|------------|-----------------------------|--------|---------------|-------|-------|-------|--------|-----------------|--|

| Syntax     | Action                      | (hex)  | 6502          | 65C02 | 65816 | bytes | cycles | Addressing Mode |  |

| CLC        | Clear Carry                 | 18     | х             | х     | х     | 1     | 2      | Implied         |  |

| SEC        | Set Carry                   | 38     | х             | х     | х     | 1     | 2      | Implied         |  |

| CLD        | Clear Decimal               | D8     | х             | х     | х     | 1     | 2      | Implied         |  |

| SED        | Set Decimal                 | F8     | х             | х     | х     | 1     | 2      | Implied         |  |

| CLI        | Enable hardware interrupts  | 58     | х             | х     | х     | 1     | 2      | Implied         |  |

| SEI        | Disable hardware interrupts | 78     | х             | х     | х     | 1     | 2      | Implied         |  |

| CLV        | Clear Overflow              | B8     | х             | х     | х     | 1     | 2      | Implied         |  |

| REP #const | Reset status bits           | C2     |               |       | х     | 2     | 3      | Immediate       |  |

| SEP #const | Set status bits             | E2     |               |       | х     | 2     | 3      | Immediate       |  |

# 1.3.2 - Compare Accumulator

### Compare Accumulator with Memory

CMP subtracts the data at the address in the operand from the contents of the accumulator, setting the n, z & c flags based on the result. The Accumulator & Memory are unaffected by this operation.

### Data size

On all processors, the data added from memory is 8-bit. However, for 16-bit processors with the m flag is clear then the data added is 16-bit with the low-order 8-bits at the effective address and the high-order 8-bits at the effective address plus one.

#### Flags Affected

| Flags n z c |       |   |   |   |   |   |   |   |   |

|-------------|-------|---|---|---|---|---|---|---|---|

|             | Flags | n | - | - | - | - | - | z | С |

- **n** Set if most-significant bit of result is set

- z Set if result is zero

- c Set if register value greater than or equal or Cleared if less than memory value

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                 |                                     |

|-----------------------|--------|--------|---------|-------|----------------|----------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles               | Addressing Mode                     |

| CMP #const            | C9     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2</sup>       | Immediate                           |

| CMP addr              | CD     | х      | х       | х     | 3              | 4 <sup>2</sup>       | Absolute                            |

| CMP long              | CF     |        |         | х     | 4              | 5 <sup>2</sup>       | Absolute Long                       |

| CMP dp                | C5     | х      | х       | х     | 2              | 3 <sup>2, 3</sup>    | Direct Page                         |

| CMP ( <i>dp</i> )     | D2     |        | х       | х     | 2              | 5 <sup>2, 3</sup>    | Direct Page Indirect                |

| CMP [dp]              | C7     |        |         | x     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long           |

| CMP addr,X            | DD     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed X                  |

| CMP long,X            | DF     |        |         | x     | 4              | 5 <sup>2</sup>       | Absolute Long Indexed X             |

| CMP addr,Y            | D9     | х      | х       | х     | 3              | 4 <sup>2, 4</sup>    | Absolute Indexed Y                  |

| CMP dp,X              | D5     | х      | х       | x     | 2              | 4 <sup>2, 3</sup>    | Direct Page Indexed X               |

| CMP ( <i>dp</i> ,X)   | C1     | х      | х       | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indexed Indirect X      |

| CMP ( <i>dp</i> ),Y   | D1     | х      | х       | x     | 2              | 5 <sup>2, 3, 4</sup> | Direct Page Indirect Indexed Y      |

| CMP [ <i>dp</i> ],Y   | D7     |        |         | х     | 2              | 6 <sup>2, 3</sup>    | Direct Page Indirect Long Indexed Y |

| CMP sr,S              | C3     |        |         | x     | 2              | 4 <sup>2</sup>       | Stack Relative                      |

| CMP ( <i>sr</i> ,S),Y | D3     |        |         | х     | 2              | 7 <sup>2</sup>       | Stack Relative Indirect Indexed Y   |

### Notes:

- 1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

- 2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

- 3. 65816: Add 1 cycle if low byte of Direct Page register is not 0

- 4. Add 1 cycle if adding index crosses a page boundary

# 1.3.3 - Compare Index Register

### Compare Index Register with Memory

The CPX & CPY instructions subtracts the data at the address in the operand from the contents of the relevant index register, setting the n, z & c flags based on the result. The register & Memory are unaffected by this operation.

The primary use of the CPX or CPY instructions is to test the value of the index register against loop boundaries.

### Data size

On all processors, the data added from memory is 8-bit. However, for 16-bit processors with the m flag is clear then the data added is 16-bit with the low-order 8-bits at the effective address and the high-order 8-bits at the effective address plus one.

### Flags Affected

| Flags | n | - | - | - | - | - | z | с |

|-------|---|---|---|---|---|---|---|---|

- **n** Set if most-significant bit of result is set

- z Set if result is zero

- c Set if register value greater than or equal or Cleared if less than memory value

#### Instructions

|               | Opcode | Availabl | le on: |       | # of           | # of              |                 |

|---------------|--------|----------|--------|-------|----------------|-------------------|-----------------|

| Syntax        | (hex)  | 6502     | 65C02  | 65816 | bytes          | cycles            | Addressing Mode |

| CPX #const    | EO     | х        | х      | х     | 2 <sup>1</sup> | 2 <sup>2</sup>    | Immediate       |

| CPX addr      | EC     | х        | х      | х     | 3              | 4 <sup>2</sup>    | Absolute        |

| CPX dp        | E4     | х        | х      | х     | 2              | 3 <sup>2, 3</sup> | Direct Page     |

| CPY #const    | C0     | х        | х      | х     | 2 <sup>1</sup> | 2 <sup>2</sup>    | Immediate       |

| CPY addr      | CC     | х        | х      | х     | 3              | 4 <sup>2</sup>    | Absolute        |

| CPY <i>dp</i> | C4     | х        | х      | х     | 2              | 3 <sup>2, 3</sup> | Direct Page     |

### Notes:

1. 65816: Add 1 byte if m=0 (16-bit memory/accumulator)

2. 65816: Add 1 cycle if m=0 (16-bit memory/accumulator)

## 1.3.4 - Branch

Perform a test & branch based on that test

The branch instructions perform a test against one of the processor's flags. Depending on the instruction a branch is taken if it is either clear or set.

If the branch is taken, a 1-byte signed displacement in the second byte of the instruction is sign-extended to 16-bits and added to the Program Counter. If the branch is not taken then the instruction immediately following the 2-byte instruction is executed.

The allowable range of the displacement is -128 to +127 from the instruction immediately following the branch.

## BCC - Branch if Carry Clear

BCC tests the Carry flag and branches if it is clear.

It can be used in several ways:

- Test the result of a shift into the carry

- Determine if the result of a comparison is less than

Some assemblers accept BLT (Branch if Less Than) as an alternate mnemonic for BCC.

### BCS - Branch if Carry Set

BCS tests the Carry flag and branches if it is set.

It can be used in several ways:

- Test the result of a shift into the carry

- Determine if the result of a comparison is greater than or equal

Some assemblers accept BGE (Branch if Greater Than or Equal) as an alternate mnemonic for BCS.

### BEQ - Branch if Equal

BEQ tests the Zero flag and branches if it is set.

It can be used in several ways:

- Test the result of a comparison is equal

- Test the result of an Increment or Decrement operation is zero, useful in loops.

- Test the value just loaded is zero

- Test the result of an arithmetic operation is zero

### BNE - Branch if Not Equal

BNE tests the Zero flag and branches if it is clear.

It can be used in several ways:

- Test the result of a comparison is not equal

- Test the result of an Increment or Decrement operation is not zero

- Test the value just loaded is not zero

- Test the result of an arithmetic operation is not zero

## BMI - Branch if Minus

BMI tests the Negative flag and branches if it is set. The high bit of the value most recently affected will set the N flag. On 8-bit operations this is bit 7. On 16-bit operations (65816 only) this is bit 15.

This is normally used to determine if a two's-complement value is negative but can also be used in a loop to determine if zero has been passed when looping down through zero (the initial value must be positive)

### **BPL** - Branch if Positive

BPL tests the Negative flag and branches if it is clear. The high bit of the value most recently affected will set the N flag. On 8-bit operations this is bit 7. On 16-bit operations (65816 only) this is bit 15.

This is normally used to determine if a two's-complement value is positive or if the high bit of the value is clear.

### BVC - Branch if Overflow Clear

BVC tests the Overflow flag and branches if it is clear.

On the 6502 only 3 instructions alter the overflow flag: ADC, SBC & CLV.

On the 65C02 the BIT instruction also alters the overflow flag.

The PLP & RTI alter the flags as they restore all flags from the stack.

On the 65816 the SEP & REP instructions modify the v flag.

On some processors there's a Set Overflow hardware signal available, but on many systems there is no connection to that pin.

## BVS - Branch if Overflow Set

BVS tests the Overflow flag and branches if it is set. It has the same limitations as the BVC instruction.

Flags Affected

None.

Instructions

|               |                     | Opcode | Availa | able on: |       | # of  | # of              |                          |

|---------------|---------------------|--------|--------|----------|-------|-------|-------------------|--------------------------|

| Syntax        | Branch if           | (hex)  | 6502   | 65C02    | 65816 | bytes | cycles            | Addressing Mode          |

| BCC nearlabel | Carry clear         | 90     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BCS nearlabel | Carry set           | B0     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BEQ nearlabel | Equal, z=1          | FO     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BNE nearlabel | Not Equal, z=0      | D0     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BMI nearlabel | Minus, n=1          | 30     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BPL nearlabel | Positive, n=0       | 10     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BVC nearlabel | Overflow clear, v=0 | 50     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

| BVS nearlabel | Overflow set, v=1   | 70     | х      | х        | х     | 2     | 2 <sup>1, 2</sup> | Program Counter Relative |

### Notes:

1. Add 1 cycle if branch taken

2. Add 1 more cycle if branch taken crosses page boundary on a 6502, 65C02 or a 65816 in 6502 emulation mode (e=1)

# 1.3.5 - Jump to location

Transfer control to the address specified by the operand field.

The branch instructions sets the Program Counter to a new value from which the next instruction will be taken.

## JMP - Jump to location

The program counter is loaded with the target address. If a long JMP is executed the bank is loaded from the third byte of the address.

Some assemblers accept JML as an alternate mnemonic for JMP long.

## BRA - Branch Always

A branch is always taken, no test is performed. It is equivalent to a JMP instruction, except that as it uses a signed displacement it is only 2 bytes in length instead of 3 for JMP. In addition, because it uses displacements, code using BRA is relocatable.

The 1-byte signed displacement in the second byte of the instruction is sign-extended to 16-bits and added to the Program Counter. If the branch is not taken then the instruction immediately following the 2-byte instruction is executed.

The allowable range of the displacement is -128 to +127 from the instruction immediately following the branch.

BRA was introduced with the 65C02 processor.

### BRL - Branch Always Long

A branch is always taken, no test is performed. It is equivalent to a BRA instruction, except that BRL is a 3 byte instruction. The two bytes after the opcode form a 16-bit signed displacement from the Program Counter.

The allowable range of the displacement is anywhere within the current 64K program bank.

The advantage of BRL is that it makes code relocatable, although it is 1 cycle slower than the absolute JMP instruction.

BRL was introduced with the 65802 processor.

#### Flags Affected

None.

#### Instructions

|               | Opcode | Availa | ble on: |       | # of  | # of              |                               |

|---------------|--------|--------|---------|-------|-------|-------------------|-------------------------------|

| Syntax        | (hex)  | 6502   | 65C02   | 65816 | bytes | cycles            | Addressing Mode               |

| BRA nearlabel | 80     |        | х       | х     | 2     | 3 <sup>3</sup>    | Program Counter Relative      |

| BRL label     | 82     |        |         | х     | 3     | 4                 | Program Counter Relative Long |

| JMP addr      | 4C     | х      | х       | х     | 3     | 3                 | Absolute                      |

| JMP (addr)    | 6C     | х      | х       | х     | 3     | 5 <sup>1, 2</sup> | Absolute Indirect             |

| JMP (addr,X)  | 7C     |        | х       | х     | 3     | 6                 | Absolute Indexed Indirect     |

| JMP long      | 5C     |        |         | х     | 4     | 4                 | Absolute Long                 |

| JMP [addr]    | DC     |        |         | х     | 3     | 6                 | Absolute Indirect Long        |

### Notes:

1. Add 1 cycle if 65C02

- 2. 6502: If low byte of address is 0xFF yields incorrect result

- 3. Add 1 more cycle if branch taken crosses page boundary on a 6502, 65C02 or a 65816 in 6502 emulation mode (e=1)

# 1.3.6 - Subroutines

### Calling subroutines

The JSR & RTS instructions allows for subroutines to be implemented. The work by utilising 2 bytes on the stack consisting of the address before the next instruction to execute when the subroutine returns - not the actual address of that instruction.

On the 16-bit 65816 there are the JSL & RTL instructions. These use 3 bytes on the stack. The extra byte is the return bank address. Like RTS the address on the stack is the address before the next instruction not the actual instruction

For Interrupt routines there's the RTI instruction. That instruction is on the Interrupt page.

# JSR - Jump to Subroutine

Transfer control to a subroutine, pushing the return address onto the stack. The 16-bit address placed on the stack is the address of the 3rd byte of the instruction, not the address of the next instruction.

Subroutines called by JSR must return using the RTS instruction.

Some assemblers recognise JSR as an alternate to the 65816 JSL instruction where if the address is greater than &FFFF then the 24 bit JSL instruction is used instead.

## RTS - Return from Subroutine

Returns from a subroutine called by JSR. It pulls the 16-bit program counter from the stack, incrementing it by one so that the next instruction is the one immediately after the calling JSR instruction.

# JSL - Jump to Subroutine Long

Transfer control to a subroutine, pushing the return address onto the stack. The 24-bit address placed on the stack is the address of the 4th byte of the instruction, not the address of the next instruction.

Subroutines called by JSL must return using the RTL instruction.

# RTL - Return from Subroutine Long

Returns from a subroutine called by JSL. It pulls the 24-bit program counter from the stack, incrementing it by one so that the next instruction is the one immediately after the calling JSL instruction.

Flags Affected

None.

Instructions

|                       | Opcode | Availab | le on: |       | # of  | # of   |                           |

|-----------------------|--------|---------|--------|-------|-------|--------|---------------------------|

| Syntax                | (hex)  | 6502    | 65C02  | 65816 | bytes | cycles | Addressing Mode           |

| JSL long              | 22     |         |        | х     | 4     | 8      | Absolute Long             |

| JSR addr              | 20     | х       | х      | х     | 3     | 6      | Absolute                  |

| JSR ( <i>addr</i> ,X) | FC     |         |        | х     | 3     | 8      | Absolute Indexed Indirect |

| RTL                   | 6B     |         |        | х     | 1     | 6      | Implied                   |

| RTS                   | 60     | х       | х      | х     | 1     | 6      | Implied                   |

# 1.4 - Registers

Register operations

### 1.4.1 - LDA

Load Accumulator from Memory Load the accumulator with data from memory.

On all processors, the data loaded from memory is 8-bit. However, for 16-bit processors with the m flag is clear then the data added is 16-bit with the low-order 8-bits at the effective address and the high-order 8-bits at the effective address plus one.

### Flags Affected

| Flags | n | I | I | I | I | I | z | I |

|-------|---|---|---|---|---|---|---|---|

**n** Set if most-significant bit of result is set

z Set if result is zero

#### Instructions

|                       | Opcode | Availa | ble on: |       | # of           | # of                 |                                     |

|-----------------------|--------|--------|---------|-------|----------------|----------------------|-------------------------------------|

| Syntax                | (hex)  | 6502   | 65C02   | 65816 | bytes          | cycles               | Addressing Mode                     |

| LDA #const            | A9     | х      | х       | х     | 2 <sup>1</sup> | 2 <sup>2</sup>       | Immediate                           |

| LDA addr              | AD     | х      | х       | х     | 3              | 4 <sup>2</sup>       | Absolute                            |